### 3-Phase Brushless DC (BLDC) Motor Drive IC

The ECN3035F/3036F integrates BLDC Control Logic with a 3-Phase BLDC Motor Bridge Driver that directly drives IGBT/MOSFET Motor Bridges powered by Motor Supply Voltages from 50 to 380VDC at reduced motor current losses. The TOP Arm of each phase is DC-biased by an internal Charge Pump that works down to zero speed. On-Chip Brushless (electronic) commutation logic is fully integrated with analog OSC/PWM functions that permit an analog (VSP) voltage to control motor speed.

Description

- Integrated 3-Phase BLDC Motor Bridge Driver IC operating from 50 to 380VDC

- Integrated Charge Pump Constant TOP Arm bias independent of motor speed

- Integrated 3-Phase Brushless (Electronic) commutation via external Hall ICs

- All TOP and BOTTOM Arm gate drive outputs are Push/Pull

- BOTTOM Arms switch at up to 20kHz via an on-chip OSC/PWM

- Latch-Up free monolithic IC built with a high voltage Dielectric Isolation (DI) process

Functions

- Simple Variable Speed Control via a single (VSP) analog input

- PWM Speed Control without requiring a MicroController

- Tachometer Generates a (RPM/60)**x**(P/2)**x**3 Hertz speed signal (FG)

- On-Chip 7.5VDC regulator (CB) with a guaranteed External Min load (25mA)

- Over-Current protection is set by an external Sense Resistor (RS)

- Under-Voltage protection for TOP and BOTTOM Arms

### HITACHI

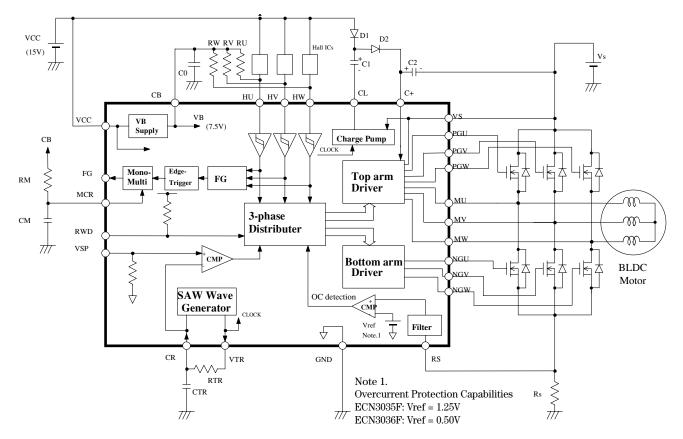

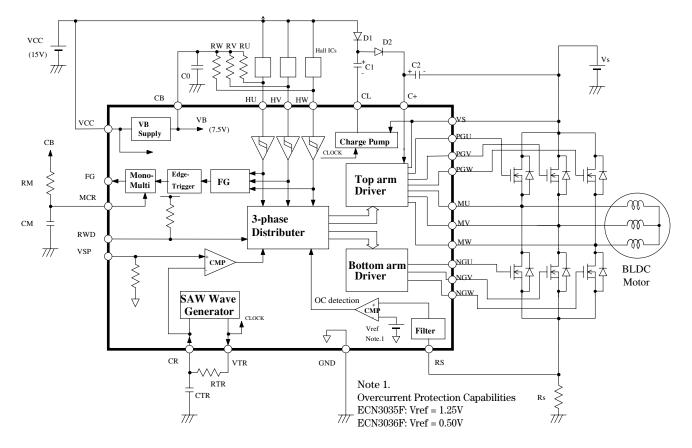

Block Diagram

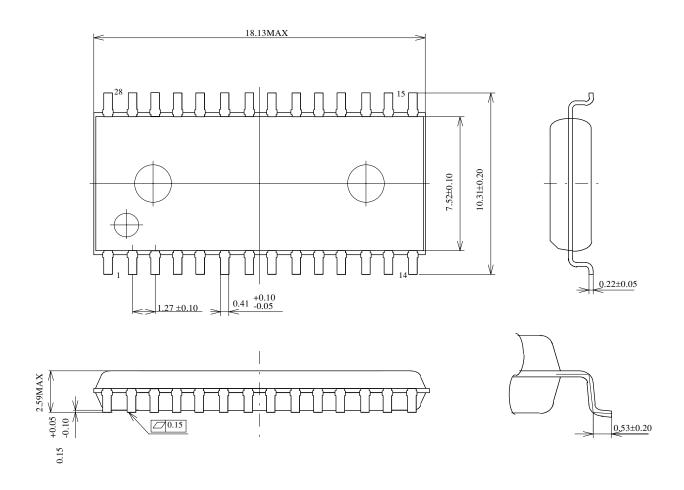

FP-28DJ(JEDEC)

Part Names and Packaging

ECN3035F / ECN3036F (Package Type:FP-28DJ (JEDEC) The ECN3035F and ECN3036F are differentiated by their Overcurrent protection capabilities.

### HITACHI

### 1. General

- (1) Type ECN3035F, ECN3036F

- (2) Application 3-Phase BLDC Motor

- (3) Structure Monolithic IC

- (4) Package FP-28DJ (JEDEC)

### 2. Maximum Allowable Ratings

| No. | Items                              | Symbols | Terminal                   | Ratings            | Unit | Condition |

|-----|------------------------------------|---------|----------------------------|--------------------|------|-----------|

| 1   | Output Device<br>Breakdown Voltage | VSM     | VS<br>MU, MV, MW           | 500                | V    |           |

| 2   | Supply Voltage                     | VCC     | VCC                        | 18                 | V    |           |

| 3   | Input Voltage                      | VIN     | VSP, RS, RWD<br>HU, HV, HW | $-0.5 \sim VB+0.5$ | V    |           |

| 4   | Operating Junction<br>Temperature  | Тјор    |                            | -20~+125           | °C   | Note 1    |

| 5   | Storage Temperature                | Tstg    |                            | -40~+150           | °C   |           |

Note 1: Thermal resistance Rj-a = 100 °C/W (When ICs are installed on a printed circuit board)

General Note: To determine appropriate deratings for these absolute maximum ratings, please refer to the "Precautions of Use" on our website.

Motor current transients (during Start & Speed-Up) may require a Soft Start circuit to limit initial currents. See: Motor Control Tech Tips, Volume 1, Issue 1 (Feb'02), "Motor Soft-Start" on our website.

Additionally, during Under and Over Voltage conditions, there may be other System Logic necessary for safe operation. See Motor Control Tech Tips, Volume 1, Issue 7 (Aug '02), "BLDC Power Bus Under/Over Voltage Protection" on our website.

| No. | Items          | Symbols | Terminal | MIN  | TYP | MAX  | Unit | Condition                          |

|-----|----------------|---------|----------|------|-----|------|------|------------------------------------|

| 1   | Supply Voltage | VS      | VS       | 50   | 325 | 380  | V    | Within allowable<br>rating at Tjop |

| 2   |                | VCC     | VCC      | 13.5 | 15  | 16.5 | V    |                                    |

### 3. Recommended Operating Conditions

### HITACHI

#### 4. Electrical characteristics

#### Suffix: T = Top arm, B = Bottom arm

Suffix \*; U, V, W Phases

|     | Inless otherwise specified, VCC =15V, VS = 325V Ta = 25°C |         |                 |                 |        |                 |      |                                                 |            |

|-----|-----------------------------------------------------------|---------|-----------------|-----------------|--------|-----------------|------|-------------------------------------------------|------------|

| No. | Items                                                     | Symbols | Terminal        | MIN             | TYP    | MAX             | Unit | Condition                                       |            |

| 1   | Standby Current                                           | IS      | VS              | -               | 1.0    | 2.5             | mA   | VSP < VSAWL                                     |            |

| 2   |                                                           | ICC     | VCC             | -               | 3.0    | 6.0             | mA   | HU=L                                            |            |

| 3   | Output Source Current                                     | IO+T    | PG*             | 30              | 50     | 100             | mA   | 20V between C+ and PG*                          |            |

| 4   |                                                           | IO+B    | NG*             | 100             | 200    | 300             | mA   | 10V between VCC a                               | and NG*    |

| 5   | Output Sink Current                                       | IO-T    | PG*             | 100             | 200    | 300             | mA   | 10V between PG* as                              | nd M*      |

| 6   |                                                           | IO-B    | NG*             | 100             | 200    | 300             | mA   | 10V between NG* a                               | nd GND     |

| 7   | High Level Output<br>Voltage                              | VOHT    | C+, PG*         | -               | -      | 0.2             | v    | Between C+ and<br>PG* Voltage                   | IO =<br>0A |

| 8   |                                                           | VOHB    | VCC, NG*        | -               | -      | 0.2             | v    | Between VCC and<br>NG* Voltage                  |            |

| 9   | Low Level Output<br>Voltage                               | VOLT    | PG*, M*         | -               | -      | 0.2             | V    | Between PG* and<br>M* Voltage                   |            |

| 10  | )                                                         | VOLB    | NG*, GND        | -               | -      | 0.2             | V    | Between NG* and<br>GND Voltage                  |            |

| 11  | Output Resistance at<br>VTR terminal                      | RVTR    | VTR             | -               | 200    | 400             | Ω    | IVTR = 1mA                                      |            |

| 12  | Amplitude Level of                                        | VSAWH   | CR              | 4.9             | 5.4    | 6.1             | V    | Note 2                                          |            |

| 13  | SAW wave                                                  | VSAWL   | CR              | 1.7             | 2.1    | 2.5             | V    |                                                 |            |

| 14  | Amplitude of SAW wave                                     | VSAWW   | CR              | 2.8             | 3.3    | 3.8             | v    | Note 5                                          |            |

| 15  | Reference Voltage for                                     | Vref    | RS              | 1.10            | 1.25   | 1.35            | V    | Only for ECN30                                  | )35F       |

|     | Over Current detection                                    |         |                 | 0.45            | 0.50   | 0.55            | V    | Only for ECN30                                  | )36F       |

| 16  | Input Voltage                                             | VIH     | HU,HV,HW        | 3.5             | -      | -               | V    |                                                 |            |

| 17  |                                                           | VIL     | RWD             | -               | -      | 1.5             | V    |                                                 |            |

| 18  | Input Current                                             | IIH     | VSP             | -               | -      | 50              | uA   | VSP = 5.0V<br>Note 1<br>Pull Down Resistant     | ce         |

| 19  |                                                           | IIL     | HU,HV,HW<br>RWD | -100            | -      | -               | uA   | HU,HV,HW,RWD=0V<br>Note 1<br>Pull Up Resistance |            |

| 20  | VB Output Voltage                                         | VB      | CB              | 6.8             | 7.5    | 8.2             | V    | IB = 0mA                                        |            |

| 21  | VB Output Current                                         | IB      | CB              | 25              | -      | -               | mA   | delta VB $\leq 0.2$ V                           | r          |

| 22  | Output Resistance at<br>FG terminal                       | RFG     | FG              | -               | 250    | 400             | Ω    | Note 3<br>IFG = 1mA                             |            |

| 23  | Reference Voltage for<br>FG pulse                         | Vref2   | MCR             | VB×2/3<br>×0.95 | VB×2/3 | VB×2/3<br>×1.05 | V    | Note 4                                          |            |

| 24  | Charge Pump Voltage                                       | VCP     | C+, VS          | 13.3            | 14.5   | -               | V    | At Stand-By N                                   | ote 6      |

Note 1. The pull up resistance and the pull down resistance are typically  $200 k\Omega$ .

- Note 2. See Note 2 in item 6 for determining the frequency of the SAW wave.

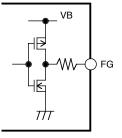

- Note 3. The equivalent circuit at FG terminal is shown in Fig. 2.

- Note 4. See Note 3 in item 6 for determining the FG output pulse width.

- Note 5. The amplitude of SAW (VSAWW) is determined by the following equation: VSAWW = VSAWH VSAWL (V)

- Note 6. The charge pump voltage (VCP) is determined by the voltage between C+ and VS.

Figure 2 Equivalent circuit around FG

### HITACHI

### 5. Function

#### 5.1 Truth Table

|     | Input |    |    | UP  | U Phase |     | V Phase |     | Phase  |

|-----|-------|----|----|-----|---------|-----|---------|-----|--------|

| RWD | HU    | HV | HW | Тор | Bottom  | Тор | Bottom  | Тор | Bottom |

| Н   | Н     | L  | Н  | L   | Н       | Н   | L       | L   | L      |

| Н   | Н     | L  | L  | L   | Н       | L   | L       | Н   | L      |

| Н   | Н     | Н  | L  | L   | L       | L   | Н       | Н   | L      |

| Н   | L     | Н  | L  | Н   | L       | L   | Н       | L   | L      |

| Н   | L     | Н  | Н  | Н   | L       | L   | L       | L   | Н      |

| Н   | L     | L  | Н  | L   | L       | Н   | L       | L   | Н      |

| L   | Н     | Н  | L  | L   | L       | Н   | L       | L   | Н      |

| L   | Н     | L  | L  | Н   | L       | L   | L       | L   | Н      |

| L   | Н     | L  | Н  | Н   | L       | L   | Н       | L   | L      |

| L   | L     | L  | Н  | L   | L       | L   | Н       | Н   | L      |

| L   | L     | Н  | Н  | L   | Н       | L   | L       | Н   | L      |

| L   | L     | Н  | L  | L   | Н       | Н   | L       | L   | L      |

| -   | L     | L  | L  | L   | L       | L   | L       | L   | L      |

| -   | Н     | Н  | Н  | L   | L       | L   | L       | L   | L      |

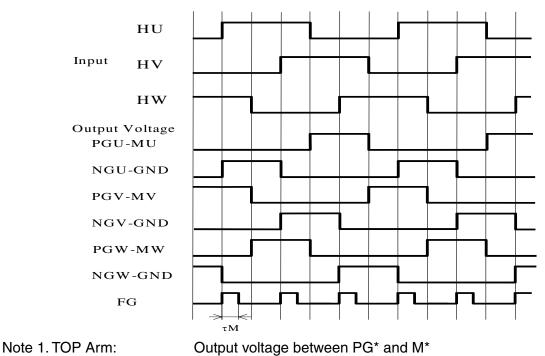

### 5.2 Timing chart (RWD = H)

BOTTOM Arm: Output voltage between NG\* and GND.

Note 2. It is possible to change the motor rotation direction by signalling direction on the RWD pin. To properly process a Reverse Command see: Motor Control Tech Tips, Volume 1, Issue 6 (July '02), "BLDC Safe Direction Reversal" on our website. Also item 5.7

### 5.3 PWM Operation

The PWM signal is generated by comparing the input voltage at the VSP pin with an internal SAW wave voltage (also available at the CR pin). The Duty Cycle of the resulting PWM signal is linearly controlled by VSP pin voltage: from a Min of VSAWL to the Max of VSAWH. That is, when VSP is below VSAWL, the PWM duty cycle is at the Minimum value of 0%. When VSP is above VSAWH, the PWM Duty Cycle is at the Maximum value of 100%. ECN3035/6 can operate in 2 Quadrants (only) by chopping the BOTTOM Arms via this PWM Duty Cycle during the appropriate commutation times (phases). Thus, PWM Duty Cycle controls motor torque and speed.

### 5.4 Over Current Limiting Operation

Over Current is monitored via the voltage drop across an external sense resistor RS. Whenever the input voltage at the RS pin exceeds the internal Reference voltage (Vref, see line #15 in Table 4), all BOTTOM Arms are Turned-OFF. Following an Over Current event, reset is automatically attempted during each OSC period. Note, the on-chip OSC signal is available at the VTR pin. If the Over Current function is not used, the RS pin must be connected to the GL pin using less than  $100\Omega$ .

### 5.5 FG operation

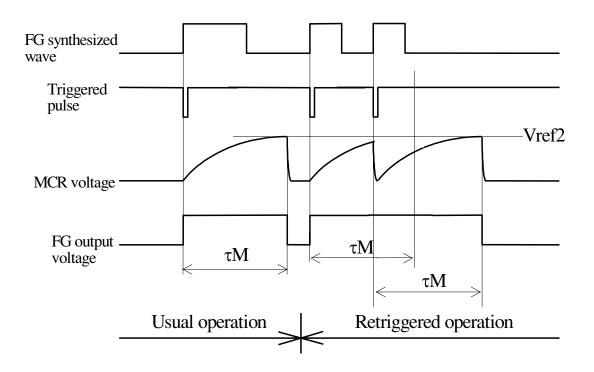

A one-shot pulse is output at the FG pin which is synchronized to the rising edge of each Hall sensor signal input at HU, HV, HW. The pulse width (tM) is set by the R and C at the MCR pin. This circuit has a retrigger feature which keeps the FG signal high whenever a trigger is input during the high time of any FG output. The frequency (in Hertz) of this motor shaft Tachometer signal is equal to (RPM/60)x(P/2)x3.

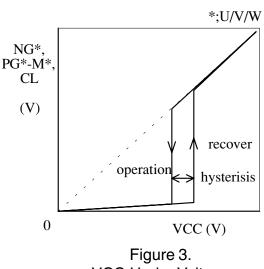

### 5.6 VCC Under Voltage Detection Operation When VCC drops below Low Voltage Shut Down (LVSD), all Arm operations and the Charge Pump are forced to Stop. The LVSD detection voltage is typically 11.5V with, a hysterisis of 0.5V.

5.7 Reverse the Rotating Direction of the Motor The rotating direction of the motor can be changed by inputing an "H" or "L" signal at the RWD pin. However, do NOT change this signal while the motor is at speed as that may cause a short through of the output Switch Device. However, it is OK to change the RWD logic input signal if the VSP analog input voltage is below VSAWL(1.7V typ). For a more complete discussion of motor speed reversal see: Motor Control Tech Tips, Volume 1, Issue 6 (July'02), "BLDC Safe Direction Reversal" on our website.

HITACHI

VCC Under Voltage Protection Hysteresis

| 6 | 6.1 External | Parts             |

|---|--------------|-------------------|

| Г | Component    | Recommended Value |

6. Standard Application

| Component | Recommended Value                                 | Usage                                      | Remark                     |

|-----------|---------------------------------------------------|--------------------------------------------|----------------------------|

| C0        | At least 0.22 μF                                  | Filters the Internal<br>Power Supply (VB). | Stress voltage is VB       |

| C1, C2    | $1.0 \ \mu F \pm 20\%$                            | Holds the Charge Pump<br>Voltage           | Stress voltage is VCC      |

| D1, D2    | Hitachi DFG1C6(glass mold)<br>or equivalent parts | Charge Pump                                | 600V / 1.0A<br>trr ≤ 100ns |

| RS        | Note 1                                            | Sets Over Current Limit                    |                            |

| CTR       | 1800 pF ± 5%                                      | Scales the PWM                             | Note 2                     |

| RTR       | 22 kΩ ± 5%                                        | Frequency                                  |                            |

| RU,RV,RW  | 5.6 kΩ ± 5%                                       | Pull up resistance                         |                            |

| CM        | More than 1000pF                                  | These set the Output                       | Note 3                     |

| RM        | More than 10 kΩ                                   | Pulse width at FG pin                      |                            |

Note 1. The start up current is limited by the following equation. IO = Vref / Rs (A)

Note 2. The PWM frequency is approximately determined by the following equation. At the recommended Value of CR, the IC has an equivalent error of about 10%. fPWM = -1 / (2CxRxLn[1-(3.5/5.5)]); Where, Ln is the Natural Logarithm = 0.494 / (CxR) (in Hz)

Note 3. The FG output pulse width is determined approximately by the following equation. tM  $\ge 10 \mu s$

tM = -(CMxRMxLn[1-VBx(2/3/VB)]) = 1.1xCMxRM (seconds)

### HITACHI

Figure 4. Block Diagram with External Parts

#### 6.2 Supply Voltage Sequence

The order for turning ON power supplies should be (1)Vcc, (2)VS then (3)VSP. The order for turning OFF should be (1)VSP, (2)VS then (3)Vcc. A useful System aid is to employ a Soft-Start circuit. See: Motor Control Tech Tips, Volume 1, Issue 1 (Feb'02), "Motor Soft-Start" on our website.

### HITACHI

#### 7. Pinout

|    | 0   |     |    |

|----|-----|-----|----|

| 1  | FG  | MU  | 28 |

| 2  | MCR | PGU | 27 |

| 3  | CR  | N.C | 26 |

| 4  | VTR | M V | 25 |

| 5  | HU  | PGV | 24 |

| 6  | ΗV  | N.C | 23 |

| 7  | ΗW  | MW  | 22 |

| 8  | VSP | PGW | 21 |

| 9  | RWD | N.C | 20 |

| 10 | R S | C + | 19 |

| 11 | СВ  | VS  | 18 |

| 12 | NGU | CL  | 17 |

| 13 | NGV | VCC | 16 |

| 14 | NGW | GND | 15 |

|    |     |     |    |

(Marking side)

#### 8. Pin Definitions

| Pin # | Symbol | Pin Definition                                                                       |

|-------|--------|--------------------------------------------------------------------------------------|

| 1     | FG     | Tachometer output signal whose frequency is (RPM/60) <b>x</b> (P/2) <b>x</b> 3 Hertz |

| 2     | MCR    | Tachometer output Pulse Width Set by these R/C values ~ (1.1) x R x C                |

| 3     | CR     | Connected Resistance/Capacitance Generate the PWM clock frequency                    |

| 4     | VTR    | Connect resistance to generate the PWM clock frequency                               |

| 5     | HU     | Input signal from the Hall IC of phase U                                             |

| 6     | HV     | Input signal from the Hall IC of phase V                                             |

| 7     | НW     | Input signal from the Hall IC of phase W                                             |

| 8     | VSP    | Input analog voltage that varies the PWM duty cycle from 0% to 100%                  |

| 9     | RWD    | Logic Input to Reverse Direction of the BLDC Motor (See Tech Tip #6)                 |

| 10    | RS     | RS voltage detect input for the on-chip Over Current limit detection                 |

| 11    | CB     | Internally regulated (VB) 7.5V Output Pin (External 25mA guarantee)                  |

| 12    | NGU    | BOTTOM Arm Gate Drive for Phase U                                                    |

| 13    | NGV    | BOTTOM Arm Gate Drive for Phase V                                                    |

| 14    | NGW    | BOTTOM Arm Gate Drive for Phase W                                                    |

| 15    | GND    | Analog ground                                                                        |

| 16    | VCC    | Analog Power Supply from External supply (15VDC +/- 10%)                             |

| 17    | CL     | Part of Charge Pump circuit (Bias supply for ALL TOP Arm drive circuits)             |

| 18    | VS     | BLDC Motor Power Bus (50VDC Min through 380VDC Max)                                  |

| 19    | C+     | Part of Charge Pump circuit (Bias supply for ALL TOP Arm drive circuits)             |

| 20    | NC     | No Connection                                                                        |

| 21    | PGW    | TOP Arm Gate Drive for Phase W                                                       |

| 22    | MW     | TOP Arm Return ("ground") Reference Rail for Phase W                                 |

| 23    | NC     | No Connection                                                                        |

| 24    | PGV    | TOP Arm Gate Drive for Phase V                                                       |

| 25    | MV     | TOP Arm Return ("ground") Reference Rail for Phase V                                 |

| 26    | NC     | No Connection                                                                        |

| 27    | PGU    | TOP Arm Gate Drive for Phase U                                                       |

| 28    | MU     | TOP Arm Return ("ground") Reference Rail for Phase U                                 |

### HITACHI

### 9. Package Dimensions

### HITACHI

#### 10. Quality Assurance

10.1 Appearance and dimension ANSI Z1.4-1993 General inspection levels II AQL 1.0%

10.2 Electrical characteristics ANSI Z1.4-1993 General inspection levels II AQL 0.65%

#### 11. Do's and Don'ts

11.1 To protect this chip from Electrical Static Discharge (ESD), the ECN 3035F/3036F should be handled in accordance with normal industry standard procedures for protection against damage due to ESD. For a more detailed discussion of this area, please refer to the web "Precautions of Use" Section 5.

11.2 Depending on local industry/market regulations, conformal coating may be required for the following pin-to-pin spacings: 16-17, 17-18, 19-21, 22-23, 25-27.

11.3 Protective function against short circuit (ex. load short, line-to-ground short or TOP/BOTTOM Arm shorts) is not built into this IC. External protection may be needed to prevent IC breakdown under these potential application conditions.

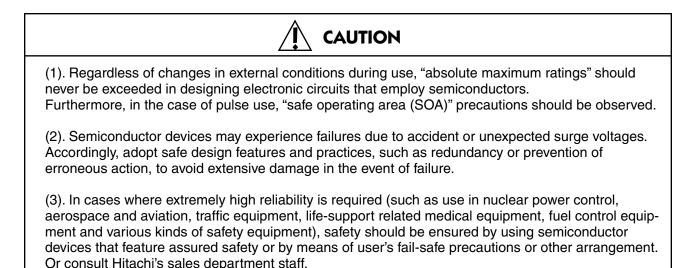

11.4 Hitachi high voltage ICs are manufactured to meet standard industrial grade reliability specifications. In cases where extremely high reliability is required (such as nuclear power control, aerospace and aviation, traffic equipment, life-support-related medical equipment, fuel control equipment and various kinds of safety equipment) system integrity must be achieved via fail-safe system design. Additionally, it is the responsibility of the designer to insure that any IC failure does not damage property or human life. Users should evaluate and consider employing the following design precautions:

a) Sufficient derating of the specifications should be utilized to minimize the possibility of failures based on the maximum ratings, operating temperature and environmental conditions.

b) Design redundancy should be applied so that application performance will be maintained even in a case of IC failure.

c) The system design should implement fail-safe design techniques to protect property and human life even where incorrect system operation is experienced.

### 12. Precautions for Safe Use

If semiconductor devices are handled in an inappropriate manner, failure may result. For this reason, be sure to read "Precautions of Use" on our website before use.

(If a semiconductor device fails, there may be cases in which the semiconductor device, wiring or wiring pattern will emit smoke or cause a fire or in which the semiconductor device will burst.)

#### 13. Notices

1. This publication contains the specifications, characteristics (in figures and tables), dimensions and handling notes concerning power semiconductor products (hereinafter called "products" to aid in the selection of suitable products.

2. The specifications and dimensions, etc. stated in this publication are subject to change without prior notice to improve product's characteristics. Before ordering, purchasers are advised to contact Hitachi's sales department for the latest version of this publication and specifications.

3. In no event shall Hitachi be liable for any damage that may result from an accident or any other cause during operation of the user's units according to this publication. Hitachi asumes no responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in this publication.

4. In no event shall Hitachi be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.

5. No license is granted by this publication under any patents or other rights of any third party, Hitachi, Ltd. or Hitachi America, Ltd.

6. This publication may not be reproduced or duplicated, in any form, in whole or in part, without the expressed written permission of Hitachi, Ltd. or Hitachi America, Ltd.

7. The products (technologies) described in this publication are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.